# Scenario-based verification of real-time systems using UPPAAL

Shuhao Li · Sandie Balaguer · Alexandre David · Kim G. Larsen · Brian Nielsen · Saulius Pusinskas

© Springer Science+Business Media, LLC 2010

**Abstract** This article proposes two approaches to tool-supported automatic verification of dense real-time systems against scenario-based requirements, where a system is modeled as a network of timed automata (TAs) or as a set of driving live sequence charts (LSCs), and a requirement is specified as a separate monitored LSC chart.

We make timed extensions to a kernel subset of the LSC language and define a tracebased semantics. By translating a monitored LSC chart to a behavior-equivalent observer TA and then non-intrusively composing this observer with the original TA-modeled realtime system, the problems of scenario-based verification reduce to computation tree logic (CTL) real-time model checking problems. When the real-time system is modeled as a set of driving LSC charts, we translate these driving charts and the monitored chart into a behaviorequivalent network of TAs by using a "one-TA-per-instance line" approach, and then reduce the problems of scenario-based verification also to CTL real-time model checking problems. We show how we exploit the expressivity of the TA formalism and the CTL query language

K.G. Larsen e-mail: kgl@cs.aau.dk

B. Nielsen e-mail: bnielsen@cs.aau.dk

S. Pusinskas e-mail: saulius@cs.aau.dk

This work has been supported by the ICT competence center CISS (Center for Embedded Software Systems) and the advanced technology platform DaNES (Danish Network for intelligent Embedded Systems).

S. Li (⊠) · A. David · K.G. Larsen · B. Nielsen · S. Pusinskas CISS, Department of Computer Science, Aalborg University, Aalborg, Denmark e-mail: li@cs.aau.dk

A. David e-mail: adavid@cs.aau.dk

S. Balaguer LSV, ENS Cachan/INRIA, Cachan Cedex, France e-mail: balaguer@lsv.ens-cachan.fr

of the real-time model checker UPPAAL to accomplish these tasks. The proposed two approaches are implemented in the UPPAAL tool and built as a tool chain, respectively. We carry out a number of experiments with both verification approaches, and the results indicate that these methods are viable, computationally feasible, and the tools are effective.

Keywords Real-time system  $\cdot$  Modeling  $\cdot$  Timed automata  $\cdot$  Scenario  $\cdot$  Live sequence chart  $\cdot$  Verification

# 1 Introduction

A model checker typically needs two inputs: a model that characterizes the state/transition behaviors of a finite state concurrent system, and a temporal logic formula that specifies the property of interest. For real-time systems, a widely used modeling formalism is timed automata (TA) [2], and the temporal logics could be CTL, LTL, TCTL, etc. Various methods, techniques and tools for model checking real-time systems have been developed over the years, and numerous successful stories of applying them to industrial projects have been reported [7].

Temporal logics such as CTL, LTL, TCTL in themselves are rich enough to formalize a wide range of user requirements such as reachability, safety, liveness and responsiveness. However, these logics are difficult to grasp by non-mathematician/logician users, and in most existing real-time model checkers such as KRONOS [42] and UPPAAL [7], they have only incomplete implementations—on one hand, their atomic propositions are interpreted over the semantic states of timed automata and cannot be event occurrences [7, 42]; and on the other hand, there are only limited or even no means for straightforward characterization of quantitative timing constraints [7, 42].

The first incompleteness as mentioned above implies that these temporal logics describe only *intra*-process (or "state/transition-based") properties, i.e., whether all states ( $\Box$ ) or at least one state ( $\Diamond$ ) along all paths (A) or at least one path (E) of the individual processes or the product process (i.e., the parallel composed system model) satisfy some particular properties. The second incompleteness implies that general form timing requirements such as  $E\Diamond_{1\leq x\leq 3}$  cannot be easily captured. Altogether, we cannot hope to use these temporal logics to characterize event synchronizations, causal relations, or timed scenarios such as "if process *B* sends message  $m_1$  to process *A*, and *C* sends  $m_2$  to *D* (in any order), then *B* **must** send  $m_3$  to *C* within 1 to 3 time units" intuitively and conveniently.

Live Sequence Chart (LSC) [12, 18] is a visual formalism for scenario-based requirement specification (in this case, an LSC chart is called a *monitored* chart). Similar to the classical Message Sequence Chart (MSC) [21], LSC also describes *inter*-process properties, i.e., how the system processes interact, collaborate and cooperate via message or rendezvous synchronizations. But beyond that, LSC makes essential extensions to MSC by adding modalities. The *existential* and *cold* (resp. *universal* and *hot*) modalities represent the provisional (resp. mandatory) requirements at global (i.e., whole chart) and local (i.e., message, condition, location and cut) levels, respectively. At the global level, an existential (resp. universal) chart specifies restrictions over at least one satisfying (resp. all possible) system runs. At the local level, for example, a cold condition may be violated and thus lead to a "graceful" chart exit, whereas a hot one must be satisfied and otherwise will indicate an error. The power of LSC lies in that a universal LSC chart can optionally contain a prechart, which specifies the scenario which, if successfully executed (or matched), forces the system to satisfy the scenario given in the actual chart body (i.e., the main chart). Furthermore, the LSC language

is unambiguous because it has strictly defined semantics, e.g., the executable (operational) semantics [18] and the trace-based semantics [12, 27].

We envisage LSC as a nice complement to the intra-process property specification languages of existing (real-time) model checkers:

- Intuitiveness. As a visual formalism, LSC is more intuitive in capturing complex user requirements than the text-form temporal logics;

- Scenario characterization. Compared with many temporal logics whose atomic propositions are restricted to be state formulas, LSC has the necessary language constructs (e.g., message and conditional synchronization) to describe process interactions and thus enable the characterization of a variety of causality and non-trivial scenarios. In particular, LSC can be extended to describe timed scenarios;

- Counterexample display. In conventional temporal logic model checking, even if a counterexample is due to an inappropriately specified requirement on a correct system model, one has to debug the model to find out the specification error. LSC improves on this by providing the possibility of tracing the counterexamples also back to the visual, scenario-based requirement specifications, and thus facilitates the debugging of both the system models and the user requirements.

In addition to being used as a requirement specification language, LSC can also serve as a scenario-based behavioral modeling language (in this case, each LSC chart is called a *driving* chart). A communicating system can be modeled as a set of driving LSC charts, which we call an *LSC system* (*LS*). Scenario-based modeling using LSCs enjoys the advantage of piecewise incremental construction of system models, i.e., new pieces of scenarios can be added into the models during the development process. However, to check whether an LSC-modeled system satisfies a scenario-based requirement is difficult due to the need to consider both the explicitly specified and implicitly allowed behaviors in each scenario, and the interplays among the different scenarios. The problem becomes even more complicated for real-time systems, as time-enriched LSCs may contain subtle timing errors that are difficult to diagnose. Clearly, this verification problem needs powerful analysis methods, techniques and automated tool support.

In an LSC system, the instance lines in the charts can be viewed as parallel composed processes that interact with one another via message or rendezvous synchronizations. This in spirit resembles some formalisms and tools for concurrent system modeling and analysis. Specifically, the real-time model checker UPPAAL [7] operates on a network of interacting timed automata that communicate via handshake and broadcast synchronizations and shared-variable communications. With its features of committed locations, broadcast channels, and boolean and integer variables, UPPAAL is capable of properly minicking the behaviors of a time-enriched LSC system using timed automata. This opens up the possibility of exploiting the power of UPPAAL for simulating and analyzing scenario-based real-time system models.

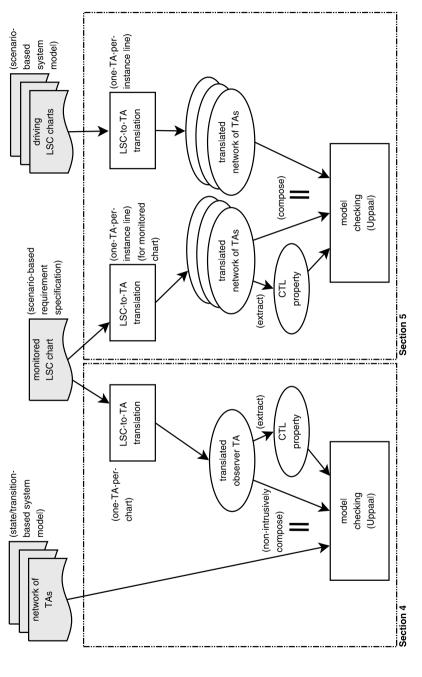

A monitored LSC chart captures the user requirement that once the prechart (if any) is successfully matched, then the main chart **must** be matched afterwards. This is a kind of liveness or responsiveness requirement. Coincidentally, the UPPAAL CTL query language has the "leads-to" property pattern  $\phi \rightsquigarrow \varphi$  which is a shorthand for  $A\Box(\phi \Rightarrow A\Diamond\varphi)$ , stating that whenever  $\phi$  is satisfied, then eventually  $\varphi$  will be satisfied. By automatically transforming a monitored chart into a behavior-equivalent observer timed automaton, we can specify a corresponding  $\phi \rightsquigarrow \varphi$  property in UPPAAL to capture the LSC requirement. By non-intrusively composing the observer timed automaton with a TA-modeled real-time system, we can achieve the effect of using a monitored chart to "spy on" the system behaviors. All these pave way to verifying real-time systems against scenario-based LSC requirements. In this article we model a real-time system as a state/transition-based system, more precisely a network of timed automata, or as an object interaction-based system, more precisely a set of driving LSC charts. We capture a scenario-based requirement that is to be verified using a separate monitored LSC chart. We aim at tool-supported automatic verification of the system against the requirement (Fig. 1). As mentioned in the previous paragraphs, we notice that the problems of verifying a state/transition-based real-time system (Fig. 1, left part) and an object interaction-based real-time system (Fig. 1, right part) against a scenario-based user requirement can both be reduced to CTL real-time model checking problems. Since UPPAAL has sophisticated data structures and efficient verification algorithms for handling timing constraints, in this article we will employ UPPAAL as our underlying verification engine.

This article is an extended version of previous work at FM'09 (Fig. 1, left part) [29]. In this article, we extend our previous work by complementing (i.e., "horizontally scaling up") the verification framework with systems being modeled as a set of driving time-enriched LSC charts (Fig. 1, right part, partly taken from [30]). We provide lemmas and proofs for the theorems in this article. We add new translation and verification methods for LSC charts under the iterative activation mode. We provide explanations on the prototype tool implementations, and report in more detail some experimental verification results.

# 1.1 Contributions

The main contributions of this article include:

- We define a kernel subset of the LSC language, make timed extensions to this subset such that it is suitable both for scenario-based behavioral modeling and for scenario-based requirement specification of real-time systems, and we define a trace-based semantics;

- We propose a behavior-equivalent translation of a monitored LSC chart to an observer timed automaton, and propose a method of non-intrusively "observing" an existing TAmodeled real-time system using this observer automaton, thus encoding the problem of verifying state/transition-based real-time systems against scenario-based requirements as a CTL real-time model checking problem. We show how these are integrated into the UPPAAL model checker;

- We propose a behavior-equivalent translation of a driving or monitored LSC chart to a network of timed automata, one for each instance line, and reduce the problem of verifying object interaction-based real-time systems against scenario-based requirements to CTL real-time model checking problems. We implement the LSC-to-TA translator which, together with our LSC editor and the UPPAAL model checker, constitutes a tool chain for scenario-based automatic verification; and

- We conduct experimental evaluations of the proposed approaches, and report the results.

# 1.2 Organization

Section 2 shows how to model and specify real-time systems using timed automata and temporal logics, respectively, and why scenario-based approaches may come in handy. In Sect. 3 we define the notations, syntax and semantics of our time-enriched LSC chart. Sections 4 and 5 show how to verify a state/transition-based real-time system and an object interactionbased real-time system against a scenario-based requirement, respectively. Section 6 reports the tool implementations and experimental evaluations of the proposed approaches. Section 7 shows how to horizontally scale up the LSC-to-TA translation methods from invariant mode charts to iterative mode charts. Section 8 discusses some related work on scenariobased verification of real-time systems. Finally, Sect. 9 concludes this article.

Fig. 1 The overall framework of scenario-based verification of real-time systems

# 2 Modeling and specification of real-time systems

2.1 Timed automata and computation tree logic

Timed automata (TA) is a popular visual formalism for modeling the state/transition-based behaviors of dense real-time systems. According to Alur and Henzinger [3], the underlying philosophy of TA is that a real-time system can be viewed as a discrete system with clock variables:

- The discrete system is represented as a finite directed graph, where each vertex represents a (control) *location*, and each edge represents an instantaneous *switch* (or discrete jump); and

- The system has a finite set of *clocks* which increase at the same speed and can be reset. Each clock variable keeps track of the elapsed time since last time this clock was reset. Clock variables can be used in boolean expressions to guard the instantaneous switches. Each location may be associated with a clock constraint called *invariant*, specifying the condition under which time can still elapse in this location.<sup>1</sup>

To describe a system which consists of a number of concurrently running processes, a network of timed automata can be constructed, one for each process. These automata are composed in parallel using the operator  $\parallel$ . Different automata in the system can synchronize on their common actions [2], and the product automaton has an interleaved execution semantics.

Timed automata in its original form [2] are a simple, concise and yet expressive language. To better support the modeling and automatic verification of real-time systems, various syntactic sugar and extensions are added to the TA formalism. Specifically, UPPAAL [7] strengthens TA with a number of features such as boolean and bounded integer variables, variable constraints and updates, urgent and committed locations, handshake and broadcast channel synchronizations, shared variable communications, etc. Here an *urgent* location is a location where time is frozen (i.e., once an urgent location is entered, it should be exited with zero time delay); and a *committed* location is a special urgent location where the outgoing transitions have higher priority to be taken than those from non-committed ones (Fig. 2(c), the "C"-marked location).

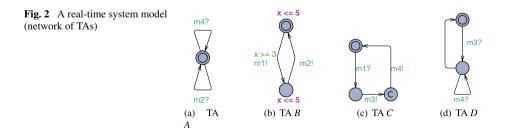

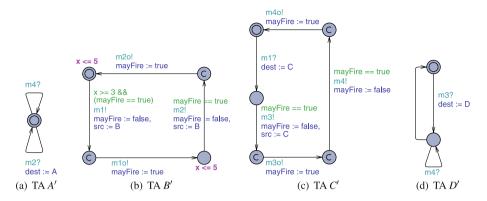

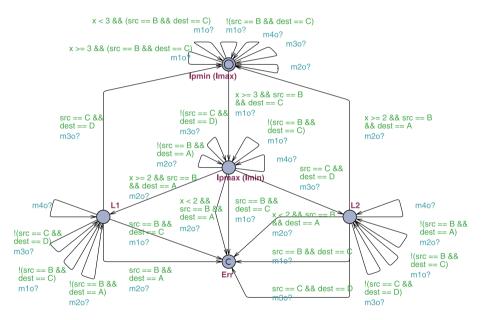

Fig. 2(a)–(d) give an example of a network of TAs in UPPAAL.

Requirements on TA-modeled real-time systems can be specified using temporal logics such as CTL, LTL or timed variants thereof. For example, UPPAAL uses a fragment of the

<sup>&</sup>lt;sup>1</sup>Pragmatically, location invariants are used to allow the system to stay in a location for a limited period of time, and then force it to leave that location.

CTL logic as its property specification language. Atomic propositions take the form:

*ap* ::= *automaton.location* | *guard\_on\_clocks* | *guard\_on\_variables*,

and properties can be specified using a number of patterns:

- reachability ( $\mathsf{E}\Diamond\phi$ );

- safety  $(A\Box\phi, E\Box\phi)$ ; and

- liveness properties ( $A \Diamond \phi, \phi \rightsquigarrow \varphi$ ).

In particular the *leads-to* (*responsiveness*) property  $\phi \rightsquigarrow \varphi$  is a shorthand for  $A \Box (\phi \Rightarrow A \Diamond \varphi)$ , stating that whenever  $\phi$  is satisfied, then eventually  $\varphi$  will be satisfied.

## 2.2 Scenario-based approaches

Although a lot of properties can be specified by using the above-mentioned property patterns, many others still cannot. Consider a user requirement on the TAs in Fig. 2:

If we observe that process B sends message  $m_1$  to process C when clock x is no less than 3, then afterwards (and before  $m_1$  can be observed again) we **must** observe that B sends  $m_2$  to A when x is no less than 2, and C sends  $m_3$  to D (in any order).

This requirement cannot be specified as a UPPAAL CTL formula or a KRONOS TCTL formula. The reason is that the atomic propositions, which are restricted to be state propositions, do not characterize message passing directly. In other words, they lack the necessary mechanisms for specifying the process interactions and scenarios.

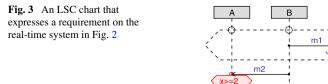

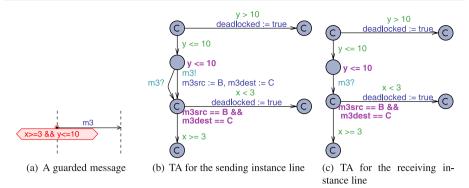

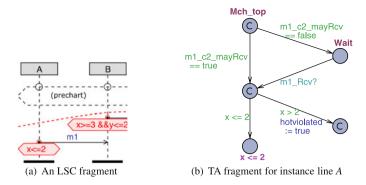

Live Sequence Chart (LSC) is a scenario-based requirement specification language. After extending the LSC language with TA-like clock variables and clock constraints, we notice that the above requirement can be easily captured using LSC (Fig. 3). For instance, the first block of diagrammatic elements  $\{m_1, x \ge 3\}$  means that: when message  $m_1$  in the real-time system model is observed, the value of clock x should be no less than 3 at this moment; and if this is the case, then the monitored execution continues, otherwise the prechart (Fig. 3, the outer dashed hexagon) is cold-violated and exited, indicating that this "premise" is not satisfied.

Thanks to its *liveness* feature and executable semantics, LSC can also be used to model the scenario-based interaction behaviors of communicating systems. In this case, each LSC chart describes a piece of the "**if** (something happens) **then** (some other thing **must** happen)" style behaviors. A number of driving charts collectively constitute the system model. They characterize how the system processes should interact and collaborate. By allowing LSC to be used both for requirement specification and for system modeling, we may carry out scenario-based validation activities in a much earlier stage of the software development cycle, thus making it possible for developers to focus more efforts on programming/validationin-the-large rather than programming/validation-in-the-small.

ma

# 3 Live Sequence Chart: timed extensions and semantics

# 3.1 Notations and syntax

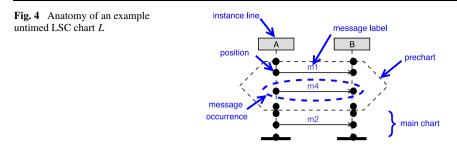

In this article, LSC in its simplest form is a message-only untimed chart, i.e., there are only language elements of instance lines, locations, messages and precharts/main charts (Fig. 4).

We make the *synchrony* hypothesis, i.e., system events consume no real time and time may elapse only between events. In this way message synchronizations will be instantaneous, i.e., the sending and receiving of a message are assumed to happen at the same moment in time. Therefore the terms of *message* and (message sending or receiving) *event* will be used interchangeably.

An LSC chart has a role, a type and an activation mode. In this article we consider the roles of:

- property specification, i.e., a monitored chart will just "listen to" the messages and read the clock variables in the original system models, but never emit messages to or reset the clocks in those models; and

- system modeling, i.e., a driving chart can emit messages and/or reset the clocks when it needs to do so.

A monitored LSC chart could be of the *universal* or *existential* type, whereas a driving chart can only be of the universal type. Since an existential chart is in nature similar to a Message Sequence Chart, in this article we will mainly be interested in universal charts. A driving or monitored universal chart consists of:

- a main chart (Mch), which specifies what should happen in order for this universal chart to be satisfied (Fig. 4, lower part of the chart<sup>2</sup>); and optionally

- a prechart (Pch), which specifies the "premise" whose satisfaction triggers the main chart and forces it to be satisfied (Fig. 4, upper part of the chart, i.e., the dashed hexagon area).

If a universal chart has no prechart, then it can be simply treated as having a satisfying prechart. In this article we assume that a universal chart has a prechart. Furthermore, an existential chart consists of only a main chart.

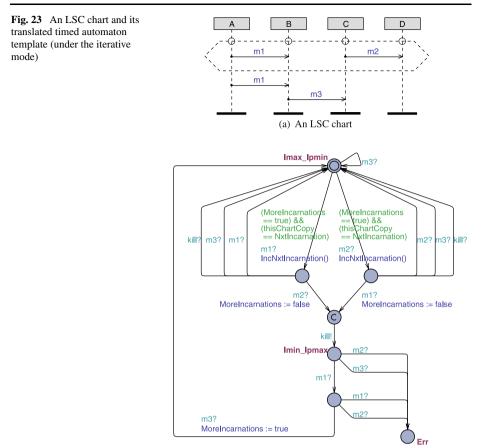

A universal chart has an *activation mode* which determines how often a chart should be activated. In this article we consider:

- the *invariant* mode, i.e., the prechart is being constantly matched for in the message stream (i.e., for any arriving message, in addition to being monitored by existing prechart copies, it will initiate a new prechart copy), and the main chart will be activated (i.e., a live chart copy will be incarnated and then enforced) whenever the prechart is successfully completed; and

- the *iterative* mode, i.e., as long as the main chart is currently active, the prechart will not be monitored for further satisfaction (until the current "iteration" of the main chart is over).

In the rest of this section and Sects. 4–6, we consider only the invariant mode LSC charts and their translations. The case of the iterative activation mode will be addressed in Sect. 7.

<sup>&</sup>lt;sup>2</sup>In the original definition of LSC [18], the main chart of a universal chart should be enclosed within a solid rectangle borderline, whereas that of an existential chart should be within a dashed borderline. For brevity, in this article we omit the borderlines of universal charts. Since no existential chart examples are given in this article, no confusion arises between existential charts and non-prechart universal charts.

## 3.1.1 Message-only untimed chart

We start with message-only untimed charts. See Fig. 4 for an example.

Each LSC chart describes a particular interaction scenario among a set of processes (or instances, or agents). Given a universal chart *L*, let I = inst(L) be the set of instance lines in *L* (Fig. 4, instance lines {*A*, *B*}). Along each instance line  $I_i \in I$  there is a finite set of "positions"  $pos(L, I_i) = \{0, 1, 2, ..., p_max_{L,I_i}\} \subset \mathbb{N}_{\geq 0}$ , which denote the points of communication, computation and synchronization (Fig. 4, black filled circles along *A* and *B*). Specifically, along each instance line  $I_i$  there are four "standard" positions  $StdPos(L, I_i) = \{Pch_top_{L,I_i}, Pch_bot_{L,I_i}, Mch_top_{L,I_i}, Mch_bot_{L,I_i}\} \subseteq pos(L, I_i)$ , denoting the entry/exit points of the prechart/main chart, respectively (Fig. 4, downward ascending positions 0, 3, 4, 6 on instance line *A*), such that:

$$-0 = Pch\_top_{L,I_i} < Pch\_bot_{L,I_i} < Mch\_top_{L,I_i} < Mch\_bot_{L,I_i} = p\_max_{L,I_i}; \text{ and} \\ -Pch\_bot_{L,I_i} + 1 = Mch\_top_{L,I_i}.$$

The positions of an existential chart *L* can be defined similarly. Since an existential chart has no prechart, an instance line  $I_i$  of it has only two "standard" positions  $Mch_top_{L,I_i}$  and  $Mch_bot_{L,I_i}$ .

A chart *location* is a position on a certain instance line of the chart. The set of all locations of chart *L* is denoted as:

$$Loc = loc(L) = \{ \langle I_i, p \rangle \mid I_i \in inst(L), p \in pos(L, I_i) \}.$$

Since a "standard" position cannot be the end point of a message, the set of all *message*anchoring locations of L is denoted as:

$$loc_M(L) = \{ \langle I_i, p \rangle \mid I_i \in inst(L), p \in pos(L, I_i) \setminus StdPos(L, I_i) \}.$$

Furthermore, we define a function  $psn : loc(L) \to \bigcup_{I_i \in inst(L)} pos(L, I_i)$  to project a location to its **position** on its instance line.

Let *L* be an LSC chart, and ML(L) be the set of **m**essage labels (or "signals", or "channels" in UPPAAL) of *L* (Fig. 4,  $\{m_1, m_2, m_4\}$ ). A message occurrence mo =  $(\langle I_i, p \rangle, m, \langle I_{i'}, p' \rangle) \in loc_M(L) \times ML(L) \times loc_M(L)$  corresponds to instance  $I_i$ , while in its position (p - 1), sending signal  $m \in ML(L)$  to instance  $I_{i'}$  at its position (p' - 1), and then arriving at positions *p* and *p'*, respectively (Fig. 4, ellipse-circled portion). We call lab(mo) = m the message label,  $head(mo) = \langle I_{i'}, p' \rangle$  and  $tail(mo) = \langle I_i, p \rangle$  the message head and tail locations, and  $src(mo) = I_i$  and  $dest(mo) = I_{i'}$  the source and destination instances, respectively. We use  $loc(mo) = \{head(mo), tail(mo)\}$  to denote the message anchoring locations. The set of all message occurrences in chart L is denoted as:

$$MO(L) \subseteq \{(\langle I_i, p \rangle, m, \langle I_{i'}, p' \rangle) \in loc_M(L) \times ML(L) \times loc_M(L) \mid p \leq Pch\_bot_{L,I_i} \Leftrightarrow p' \leq Pch\_bot_{L,I_{i'}}\}.$$

We omit the parameter L in MO(L) (and thus abbreviating it as MO) when it is clear from the context. Furthermore, the projection of MO(L) onto  $inst(L) \times ML(L) \times inst(L)$ is denoted as  $\Sigma = MA(L)$  ("message alphabet"), where each letter is a message which denotes that a particular signal is sent from one object (instance line) to another. For a given message occurrence, we may overload its "message label" to also denote the corresponding letter in  $\Sigma$ .

This article does not consider concurrent messages (i.e., we assume that any instance line does not send and/or receive two or more messages simultaneously), thus each location can be the end point of at most one message occurrence in the chart.

## 3.1.2 Time-enriched chart

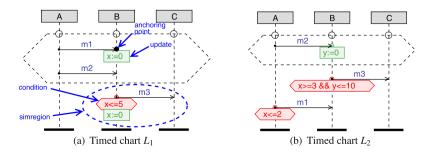

Now we continue to define our timed extensions to the above kernel subset of the LSC language. In our time-enriched LSC charts, there are further elements of (clock) variables, conditions (clock constraints), updates (clock resets) and simregions (i.e., "simultaneous regions"). Figure 5 gives two example time-enriched LSC charts (for clarity the normal positions on the instance lines are omitted).

Assume that in chart *L* there is a finite set *X* of real-valued *clock variables* that range over  $\mathbb{R}_{\geq 0}$ . A *clock valuation* is a function  $v: X \to \mathbb{R}_{\geq 0}$  that maps each clock variable to a non-negative real number, also denoted  $v \in \mathbb{R}_{\geq 0}^X$ .

Let  $d \in \mathbb{R}_{\geq 0}$ . Notation  $(v + d) : X \to \mathbb{R}_{\geq 0}$  means that the clock valuation v is shifted by d such that  $\forall x \in X . (v(x + d) = v(x) + d)$ .

A *clock constraint* is of the form  $x \bowtie n$  or  $x - y \bowtie n$  where  $x, y \in X, n \in \mathbb{Z}$ , and  $\bowtie \in \{<, \leq, =, \geq, >\}$ . Let B(X) be the set of finite conjunctions over these constraints. A *condition* (or *guard*) is an element from B(X) that spans across (and thus "anchors" on or intersects with) one or more instance lines, denoted  $g \in Loc^+ \times B(X)$ . Here  $Loc^+ = \bigcup_{i=1}^{card(I)} Loc^i$  represents the union of Cartesian products where the number of Loc's ranges from 1 to card(I) (i.e., the cardinality of I). The set of guards in a chart is denoted  $G \subset Loc^+ \times B(X)$ . The set of anchoring locations of condition g is denoted loc(g). We may omit the location information of a guard when it is not explicitly needed in the context (Fig. 5(b),  $\{x \ge 3 \land y \le 10, x \le 2\}$ ).

Fig. 5 Example time-enriched LSC charts

The LSC language constructs such as location, message and condition each have a cold/hot modality (or "temperature"). For example, the temperature of a condition  $g \in G$  is denoted *g.temp*. When *temp* is cold, the condition is enclosed in a dashed hexagon (Fig. 3,  $x \ge 3$ ); when *temp* is hot, it is enclosed in a solid hexagon (Fig. 5(a),  $x \le 5$ ). Temperature defines the criticality of a condition, and it also determines the consequence when this condition evaluates to false. While a hot condition evaluates to false, a cold condition may or may not be satisfied. When a hot condition evaluates to false, it indicates a violation of the system requirement. In contrast, a cold condition evaluating to false merely induces a "graceful" exit from the chart. The temperature of a condition may be either hot or cold in a main chart. However, it can only be cold in a prechart. The reason is that a prechart itself does not enforce anything.

In the original definition of LSC [18], many language constructs have their hot/cold modalities. For simplicity, in this article we distinguish between the cold and hot temperatures only for conditions, and assume hot as the default temperature for other constructs.

A *clock reset* is of the form x := 0 where  $x \in X$ . An *assignment* (or update) is the union of a finite set of clock resets (also written as the set of clocks to be reset) that spans across one or more instance lines, denoted  $a \in Loc^+ \times 2^X$ . The set of all assignments in the chart is denoted  $A \subset Loc^+ \times 2^X$ . The set of anchoring locations of assignment *a* is denoted *loc(a)*. The location information of an assignment may also be omitted if it is not explicitly needed in the context (Fig. 5(b), y := 0). Furthermore, we can also view  $a \in A$  as a transformer on the functions of clock valuations, and as such the new valuation of *v* after assignment *a* is denoted by v' = a(v).

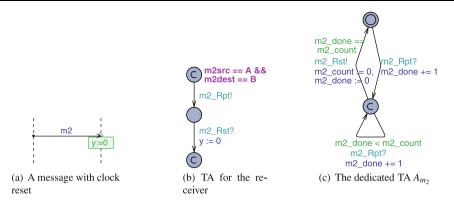

Unlike in untimed charts where a message occurs all by itself, in time-enriched LSCs, each message occurrence *mo* can be optionally associated with a condition *g* and/or an assignment *a*. Notationally the condition and/or assignment is anchored to an end point of the message (Fig. 5(a), the two anchoring points on  $m_1$  and  $m_3$ ). A message occurrence and the condition and/or assignment attached thereto (if any) constitute an atomic step of LSC execution (Fig. 5(a), the ellipse area), i.e., they take place at the same moment in time. As inspired by [25], we call such a structure of message occurrence/condition/assignment a *simultaneous region* (simregion). The intuitive meaning of message synchronization [*g*]*mo/a* from location  $\langle I_i, p \rangle$  to  $\langle I_{i'}, p' \rangle$  is that, if when *mo* occurs, the clock valuation *v* satisfies *g*, then this synchronization can fire; and immediately after the firing, *v* will be updated according to *a*.

When a simregion *s* contains a message, then *s* is called a *message simregion* (Fig. 5(a), the ellipse area). If *s* has no message occurrence, then *s* consists of a condition test, or an assignment, or both of them combined and anchored together. In this case, *s* is called a *non-message simregion* (Fig. 8(c)). For such a simregion, we adopt the As-Soon-As-Possible (ASAP) semantics for its firing, i.e., the condition test (if any) will be evaluated immediately after the execution of the previous simregion, and the update (if any) follows immediately.

When the condition, message occurrence or assignment part is missing in a simregion, we denote that part as  $\varepsilon$ . Since such an "absence" does not correspond to any location, we let  $loc(\varepsilon) = \emptyset$ .

**Definition 1** (Simregion) A simregion s is a tuple of LSC condition, message occurrence, and assignment,  $s = (g, mo, a) \in (G \cup \{\varepsilon\}) \times (MO \cup \{\varepsilon\}) \times (A \cup \{\varepsilon\})$ , which is subject to the following constraints:

- common anchoring point. If  $mo \neq \varepsilon$ , then  $(g \neq \varepsilon \Rightarrow loc(g) \cap loc(mo) \neq \emptyset) \land (a \neq \varepsilon \Rightarrow loc(a) \cap loc(mo) \neq \emptyset)$ ; if  $mo = \varepsilon$ , then  $(g \neq \varepsilon \land a \neq \varepsilon \Rightarrow loc(g) \cap loc(a) \neq \emptyset)$ ;

- non-emptiness.  $(g \neq \varepsilon) \lor (mo \neq \varepsilon) \lor (a \neq \varepsilon)$ ; and

- no overlapping with other simregions.  $\forall s' = (g', mo', a') . ((loc(g) \cup loc(mo) \cup loc(a)) \land (loc(g') \cup loc(mo') \cup loc(a')) \neq \emptyset \Rightarrow (g = g') \land (mo = mo') \land (a = a')).$

The set of all simregions in a chart is denoted  $SR \in 2^{(G \cup \{\varepsilon\}) \times (MO \cup \{\varepsilon\}) \times (A \cup \{\varepsilon\})}$ .

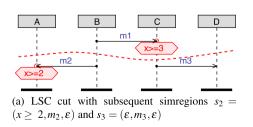

For example, in Fig. 3 there are three simregions  $s_1 = (x \ge 3, m_1, \varepsilon), s_2 = (x \ge 2, m_2, \varepsilon)$ , and  $s_3 = (\varepsilon, m_3, \varepsilon)$ . Note that for brevity here we use the message labels to represent the corresponding message occurrences.

For a simregion  $s = (g, mo, a) \in SR$ , we use  $loc(s) = loc(g) \cup loc(mo) \cup loc(a)$  to denote the set of anchoring locations of simregion *s*. For example, in Fig. 5(a) the circled simregion  $s = (x \le 5, m_3, x := 0)$  has two anchoring locations  $loc(s) = \{\langle B, 5 \rangle, \langle C, 3 \rangle\}$ .

Now that we have presented the necessary basic and composite LSC constructs, we are in place to give the following generic definition of LSC.

**Definition 2** (Live sequence chart, LSC) A *live sequence chart* is a tuple  $L = \langle I, Loc, ML, X, MO, G, A, PchBot \rangle$ , where

- I = inst(L) is the set of instance lines in L;

- Loc = loc(L) is the set of locations in L;

- ML is the set of message labels in L;

- X is the set of clocks in L;

- $SR \in 2^{(G \cup \{\varepsilon\}) \times (MO \cup \{\varepsilon\}) \times (A \cup \{\varepsilon\})}$  is the set of simregions in *L*, where:

- $G \subset Loc^+ \times B(X)$  is the set of guards;

- $MO \subset Loc \times ML \times Loc$  is the set of message occurrences;

- $A \subset Loc^+ \times 2^X$  is the set of updates; and

- $PchBot \in \{nil\} \cup Loc^+$  is the bottom location vector of the prechart. In particular when *L* has no prechart *PchBot* is *nil*.

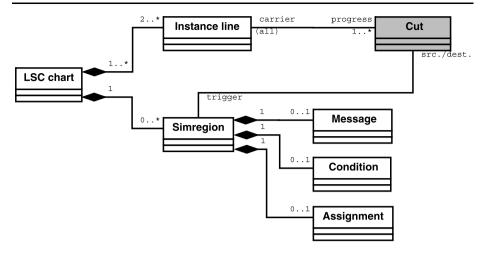

The BNF grammar for our time-enriched LSC language is given in Appendix A. The Class Diagram of our time-enriched LSC language is presented in Fig. 6, where the solid diamond lines and normal lines represent the "composition" and "association" relationships among the LSC constructs, respectively. Note that in Fig. 6 the Cut class and its relationships to other classes will be explained in Sect. 3.2.1.

# 3.2 Trace-based semantics

# 3.2.1 Semantics for a single universal chart

In an LSC chart *L*, every location is either associated with a simregion, or it is an entry/exit point of the prechart/main chart. We define a labeling function  $\lambda : loc(L) \rightarrow SR \cup \{nil\}$  to map a location of the former type to its corresponding simregion, and a location of the latter type to *nil*.

Locations in a chart L are preordered ( $\leq$ ) as follows:

- Along each instance line  $I_i$ , locations are downward increasing: location l is above  $l' \Rightarrow (l \leq l') \land \neg(l' \leq l)$ ; and

- All locations in the same simregion have the same order:  $\forall s \in SR, \forall l, l' \in loc(L)$ .  $(\lambda(l) = s) \land (\lambda(l') = s) \Rightarrow (l \leq l') \land (l' \leq l)$ .

The preorder relation  $\preccurlyeq \subseteq loc(L) \times loc(L)$  is defined as a transitive closure of  $\leq$ . For example in Fig. 5(b),  $\langle A, 0 \rangle \preccurlyeq \langle B, 1 \rangle \preccurlyeq \langle B, 5 \rangle \preccurlyeq \langle C, 4 \rangle$  is a preorder of the locations.

A cut represents all the locations along all instance lines that have been progressed so far. It is formally defined as follows.

Fig. 6 Class diagram for time-enriched LSC language

**Definition 3** (Cut of an LSC chart) A *cut* of a chart L is a set  $c \subseteq loc(L)$  of locations that span across all the instance lines in L and satisfy the properties of:

- *downward-closure*. If a location l is included in cut c, so are all of its predecessor locations:  $\forall l, l' \in loc(L)$ .  $((l \in c \land l' \preccurlyeq l) \Rightarrow l' \in c)$ ; and

- *intra-chart coordination integrity*. If a *Mch\_top* position of a certain instance line is included in the cut, then the *Mch\_top* positions of all other instance lines are also included in the cut:  $\exists l \in loc(L), I_i \in inst(L) . ((Mch_top_{L,I_i} \leq psn(l)) \land (psn(l) \leq Mch_top_{L,I_i}) \land (l \in c) \Rightarrow \forall l' \in loc(L), I_{i'} \in inst(L) . ((Mch_top_{L,I_{i'}} \leq psn(l')) \land (psn(l') \leq Mch_top_{L,I_{i'}}) \Rightarrow l' \in c)).$

For a cut *c*, we use *loc*(*c*) to denote its *frontier*, i.e., the set of locations that constitute the downward borderline progressed so far. The location where *c* "cuts" instance line  $I_k \in I$  is denoted *loc*(*c*)<sub>( $I_k$ )</sub>. For example in Fig. 5(a), if *c* is the cut when the main chart is just entered, then *loc*(*c*) = { $\langle A, 4 \rangle$ ,  $\langle B, 4 \rangle$ ,  $\langle C, 2 \rangle$ }, and *loc*(*c*)<sub>( $A \rangle$ </sub> =  $\langle A, 4 \rangle$ . The set of all cuts is denoted as *Cuts*.

Given a cut  $c \in Cuts$  and a simregion  $s \in SR$ , we say s is *enabled* at cut c (with respect to the location preorder relation), denoted  $c \xrightarrow{s}$ , if each anchoring location of s immediately follows a certain location in c. Formally,  $\forall l \in loc(s) . \exists l' \in c . ((l' \preccurlyeq l) \land \neg(l \preccurlyeq l')) \land (\nexists l'' \in loc(L) \setminus (c \cup loc(s)) . (l' \preccurlyeq l'' \land l'' \preccurlyeq l))$ . For example, in Fig. 5(a) the circled simregion is enabled at the cut when the main chart is just entered. The enabledness of message occurrences can be defined similarly.

A cut c' is an *s*-successor of cut c, denoted  $c \xrightarrow{s} c'$ , if s is enabled at c (w.r.t. the location preorder), and c' is achieved by adding the set of locations that s anchors at into c. Formally,  $c \xrightarrow{s} c' \Leftrightarrow (c \xrightarrow{s}) \land (c' = c \cup loc(s))$ .

Since a simregion triggers a new cut, this new cut and the original cut can be viewed as the destination and source cuts of the LSC advancement step, respectively. This relationship between the Cut and Simregion classes is depicted in Fig. 6. We also stress that in Fig. 6 the Cut class is singled out in shaded rectangle, because it is a semantic rather than a syntactical concept. A cut *c* is *minimal*, denoted  $\top$ , if it "cuts" each instance line at its top location; and *c* is *maximal*, denoted  $\bot$ , if it "cuts" each instance line at its bottom location. The minimal and maximal cuts of the prechart and main chart are denoted  $Pch.\top$ ,  $Pch.\bot$ ,  $Mch.\top$  and  $Mch.\bot$ , respectively. The frontiers of minimal and maximal cuts do not contain simregion anchoring points. Rather the cuts  $Pch.\bot$  and  $Mch.\bot$  each represent a requirement for compulsory synchronization of all the instance lines in the chart. Thus the preorder relation  $\preccurlyeq$  on loc(L) is extended as follows (and finally also extended to its transitive closure):

- All locations in the frontier of the same minimal or maximal cut have the same order:  $\forall c \in \{Pch.\top, Pch.\bot, Mch.\top, Mch.\bot\}, \forall l, l' \in loc(c) . (l \leq l') \land (l' \leq l).$

For example, in Fig. 3 the possible cuts are: {}, { $s_1$ }, { $s_1$ ,  $s_2$ }, { $s_1$ ,  $s_3$ }, { $s_1$ ,  $s_2$ ,  $s_3$ }, where e.g. { $s_1$ } is a shorthand for the cut where simegion  $s_1$  has just been stepped over. Clearly, cut { $s_1$ ,  $s_2$ ,  $s_3$ } is the  $s_3$ -successor of cut { $s_1$ ,  $s_2$ }.

Based on the preorder relation  $\preccurlyeq$  on loc(L), we can induce an event (message) partial order relation of the chart.

In order to define a trace-based semantics for LSC, we need to determine what is a "semantic state" of a time-enriched LSC chart. In this article we call such a semantic state an LSC configuration.

**Definition 4** (Configuration) A *configuration* of an LSC chart is a tuple (c, v), where c is a cut and v is a clock valuation.

A configuration at the minimal cut  $\top$  with all clocks assigned their initial values (e.g., 0's) is called the *initial* configuration.

In each configuration, we can check whether a next coming message violates the event partial order of the chart, and whether a next condition evaluates to true. If in the main chart the event partial order is violated or a hot condition evaluates to false, then it is a *hot violation*. In comparison, if the event partial order is violated in the prechart or a cold condition evaluates to false, then it is a *cold violation*. A hot violation means that some mandatory requirements are not satisfied and therefore there is an error in the system (e.g., an exception rather than expected message occurs in the main chart), whereas a cold violation means that some provisional requirements are not satisfied and therefore the chart can be gracefully exited (e.g., a condition in the prechart evaluates to false).

A universal chart starts from the initial configuration, advances from one configuration to a next one, until a hot violation occurs, or until the chart arrives at a maximal cut configuration and then starts all over again (i.e., to begin a next round execution).

There could be three kinds of advancement steps between two configurations (c, v) and (c', v') of a time-enriched LSC chart:

- *Message synchronization step*. Given a simregion *s* which consists of an *m*-labeled message occurrence mo ( $m \in \Sigma$ ), and optionally a condition *g* and/or assignment *a*, there is a message synchronization step  $(c, v) \xrightarrow{m} (c', v')$  if:

- (normal advancement).  $c \xrightarrow{s} c', v \models g$ , and v' = a(v); or

- (cold violation).  $c' = Pch.\top, v' = v$ , and either

- -mo is not enabled at cut c in the prechart (w.r.t. the preorder relation); or

- $v \nvDash g \land g.temp = cold;$

- Silent step. Given a similar similar which consists of a condition g and/or assignment a, there is a silent step  $(c, v) \xrightarrow{\tau} (c', v')$  if either

- (*silent advancement*).  $proj_{MO\cup\{\varepsilon\}}(s) = \varepsilon, c \xrightarrow{s} c', v \models g$ , and v' = a(v); or

- (prechart-main chart transition). ( $c = Pch. \bot, c' = Mch. \top, v' = v$ ); or

- (main chart-prechart transition). ( $c = Mch.\perp, c' = Pch.\top, v' = v$ ); or

- c' is reached because an instance line moves to its bottom location in *Pch* or *Mch* autonomously (this happens when the instance line will not interact with other instance lines before it reaches its bottom location in *Mch* or *Pch*). Formally, there exists an instance  $I_k$  such that v' = v and either

- $loc(c')_{\langle I_k \rangle} = (loc(Pch.\perp))_{\langle I_k \rangle}, psn(loc(c')_{\langle I_k \rangle}) = psn(loc(c)_{\langle I_k \rangle}) + 1, and loc(c')_{\langle I_i \rangle} = loc(c)_{\langle I_i \rangle} for all I_i \neq I_k; or$

- $loc(c')_{\langle I_k \rangle} = (loc(Mch.\perp))_{\langle I_k \rangle}, psn(loc(c')_{\langle I_k \rangle}) = psn(loc(c)_{\langle I_k \rangle}) + 1, and loc(c')_{\langle I_i \rangle} = loc(c)_{\langle I_i \rangle} for all I_i \neq I_k;$

- *Time delay step*. There is a time delay step  $(c, v) \xrightarrow{d} (c', v')$  where  $d \in \mathbb{R}_{\geq 0}$  if: c' = c, v' = v + d, and whenever there are message occurrences that are enabled at cut c (w.r.t. both the preorder relation and the guard), then after delay d there exists at least one of them that is still enabled at the same cut, i.e.,  $\exists s \in SR . (proj_{MO \cup \{\varepsilon\}}(s) \neq \varepsilon) \land (proj_{G \cup \{\varepsilon\}}(s) = g) \land (\forall d' \in [0, d] . (c \xrightarrow{s}) \land (v + d') \models g).$

Similar to the above-mentioned cold violation case, if in the main chart, an *m*-labeled message violates  $\preccurlyeq$ , or  $(v \nvDash g \land g.temp = hot)$ , then the configuration (c, v) is said to be *hot-violated*, denoted  $(c, v) \stackrel{m}{\rightarrow}$ .

**Definition 5** (Run of an LSC chart) A *run* of a time-enriched universal LSC chart is a sequence of configurations  $(c^0, v^0) \cdot (c^1, v^1) \cdots$  that are connected by the advancement steps  $(c^i, v^i) \stackrel{u_i}{\longrightarrow} (c^{i+1}, v^{i+1})$ , where  $u_i \in (\Sigma \cup \{\tau\} \cup \mathbb{R}_{>0}), i \ge 0$ .

A transition in Definition 5 carries only a single letter  $u \in (\Sigma \cup \{\tau\} \cup \mathbb{R}_{\geq 0})$ . We extend  $\rightarrow$  to  $\rightarrow^*$  such that a transition carries a (finite or infinite) word  $w \in (\Sigma \cup \{\tau\} \cup \mathbb{R}_{\geq 0})^* \cup (\Sigma \cup \{\tau\} \cup \mathbb{R}_{>0})^{\omega}$ .

Let  $\Pi$  correspond to the set of all possible messages that occur in a state/transitionbased system model (i.e., a network of timed automata), or be the set of all messages in an object interaction-based system model (i.e., a set of driving universal LSC charts). In the latter case, the message alphabet for the LSC system model  $LS = \{L_i \mid 1 \le i \le n\}$  is  $\Pi = \bigcup_{i=1}^n \Sigma_i = \bigcup_{i=1}^n MA(L_i)$ .

**Definition 6** (Satisfaction of a prechart/main chart) A timed trace  $\gamma \in (\Pi \cup \{\tau\} \cup \mathbb{R}_{\geq 0})^* \cup (\Pi \cup \{\tau\} \cup \mathbb{R}_{\geq 0})^{\omega}$  satisfies an LSC prechart or main chart *C*, denoted  $\gamma \models C$ , if its restriction  $\gamma|_{(\Sigma \cup \{\tau\} \cup \mathbb{R}_{\geq 0})}$  has a prefix  $\mu$  which is the accepted word of a run that starts from the initial configuration and arrives at a maximal cut configuration of *C*, and no prefix of it ever leads to a hot violation. Formally,  $\gamma \models C \Leftrightarrow (\exists \mu \in (\Sigma \cup \{\tau\} \cup \mathbb{R}_{\geq 0})^*, \xi \in (\Sigma \cup \{\tau\} \cup \mathbb{R}_{\geq 0})^* \cup (\Sigma \cup \{\tau\} \cup \mathbb{R}_{\geq 0})^{\omega}, v' \in \mathbb{R}_{\geq 0}^X$ .  $(\gamma|_{(\Sigma \cup \{\tau\} \cup \mathbb{R}_{\geq 0})^{\omega}, m \in \Sigma, \bullet \in Cuts \times \mathbb{R}_{\geq 0}^X$ .  $((\gamma|_{(\Sigma \cup \{\tau\} \cup \mathbb{R}_{\geq 0})^{\omega}, m \in \Sigma, \bullet \in Cuts \times \mathbb{R}_{\geq 0}^X$ .  $((\gamma|_{(\Sigma \cup \{\tau\} \cup \mathbb{R}_{\geq 0})^{\omega}, m \notin \Sigma, \bullet \in Cuts \times \mathbb{R}_{\geq 0}^X)$ .

**Definition 6a** A finite trace  $\gamma \in (\Pi \cup \{\tau\} \cup \mathbb{R}_{\geq 0})^*$  satisfies chart *C* exactly, denoted  $\gamma \Vdash C$ , iff  $\gamma$  satisfies *C*, and its restriction on  $(\Sigma \cup \{\tau\} \cup \mathbb{R}_{\geq 0})$  is the accepted word of a run that contains and ends with exactly one maximal cut configuration of *C*. Formally,  $\gamma \Vdash C \Leftrightarrow$

$$(\gamma \models C) \land \exists \mu \in (\Sigma \cup \{\tau\} \cup \mathbb{R}_{\geq 0})^*, v' \in \mathbb{R}_{\geq 0}^X . (\gamma|_{(\Sigma \cup \{\tau\} \cup \mathbb{R}_{> 0})} = \mu) \land ((\top, v^0) \xrightarrow{} (\bot, v')) \land ((\bot, v^0) \xrightarrow{} (\bot, v')$$

$$\begin{split} & \nexists \varepsilon \neq \mu' \in (\Pi \cup \{\tau\} \cup \mathbb{R}_{\geq 0})^*, \varepsilon \neq \xi \in (\Pi \cup \{\tau\} \cup \mathbb{R}_{\geq 0})^*, v'' \in \mathbb{R}_{\geq 0}{}^X . (\gamma|_{(\Sigma \cup \{\tau\} \cup \mathbb{R}_{\geq 0})} = \mu' \cdot \xi) \land ((\top, v^0) \xrightarrow{\mu'} (\bot, v'')). \end{split}$$

Now we define the satisfaction relation for a full universal chart (under the invariant activation mode):

**Definition 7** (Satisfaction of a universal LSC chart) A timed trace  $\gamma \in (\Pi \cup \{\tau\} \cup \mathbb{R}_{\geq 0})^{\omega}$ satisfies (passes) a universal chart *L*, denoted  $\gamma \models L$ , iff whenever a finite sub-trace matches the prechart, then the main chart is matched immediately afterwards. Formally,  $\gamma \models L \Leftrightarrow$  $\forall \alpha, \mu \in (\Pi \cup \{\tau\} \cup \mathbb{R}_{\geq 0})^*, \beta \in (\Pi \cup \{\tau\} \cup \mathbb{R}_{\geq 0})^{\omega}$ .  $(\alpha \cdot \mu \cdot \beta = \gamma) \land (\mu \Vdash Pch) \Rightarrow (\beta \models Mch)$ .

**Definition 7a** A timed language  $Lang \subseteq (\Pi \cup \{\tau\} \cup \mathbb{R}_{\geq 0})^{\omega}$  satisfies chart *L*, denoted  $Lang \models L$ , iff every word of *Lang* satisfies the chart. Formally,  $Lang \models L \Leftrightarrow \forall \gamma \in Lang \cdot \gamma \models L$ .

As seen above, Lang characterizes the system behaviors that respect L.

When *L* is used as a monitored chart, then for a network *S* of timed automata, we use  $S \models L$  to denote that the timed traces (language) of *S* satisfy LSC *L*.

# 3.2.2 Semantics for a set of driving universal charts

For an LSC system *LS* which consists of a set of driving universal charts  $L_1, L_2, ..., L_n$ , we denote a *cut vector* of *LS* by  $\bar{c} = (c_1, c_2, ..., c_n)$ , and a *valuation* of all of the clock variables in *LS* by v. Each member cut of  $\bar{c}$  is denoted by  $c_i = (\bar{c})_i$ ,  $1 \le i \le n$ . We call  $(\bar{c}, v)$  a global configuration of *LS*.

Let  $(\bar{c}, v)$  be a global configuration of an LSC system *LS*. Assume that there are message occurrences  $mo_1, \ldots, mo_k$   $(1 \le k \le n, \text{ each in a different chart)}$  that are simultaneously enabled at  $((\bar{c})_1, v), \ldots, ((\bar{c})_k, v)$ , and that these message occurrences are the same message (they have exactly the same message label and the same source and destination instances), i.e.,  $\exists m \in \Pi, L_j \in LS, I_a, I_b \in inst(L_j) . \forall 1 \le i \le k . (lab(mo_i) = m) \land (src(mo_i) = I_a) \land (dest(mo_i) = I_b)$ . In this case, these identically labeled message occurrences are said to be *enabled* at global configuration  $(\bar{c}, v)$  w.r.t. their respective preorder relations.

Given a global configuration  $(\bar{c}, v)$  of *LS* and a message  $m \in \Pi$ , there is a message synchronization step  $(\bar{c}, v) \xrightarrow{m} (\bar{c}', v')$  in *LS* if:

- A maximal set of *m*-labeled message occurrences are enabled at  $(\bar{c}, v)$ , and there is no chart  $L_i$  whose local configuration  $((\bar{c})_i, v)$  will be hot-violated by an *m*-labeled message. In this case, for all charts  $L_j$  that have an *m*-labeled message occurrence enabled at  $(\bar{c}, v)$ , the  $\stackrel{m}{\rightarrow}$  message synchronization steps will occur simultaneously; and

there is a silent step  $(\bar{c}, v) \xrightarrow{\tau} (\bar{c}', v)$  in LS if:

- There is a chart  $L_i$  such that  $((\bar{c})_i, v) \xrightarrow{\tau} ((\bar{c}')_i, v)$ . In this case, for all  $j \neq i$ , we have  $\bar{c}'_i = \bar{c}_i$ ; and

there is a time delay step  $(\bar{c}, v) \xrightarrow{d} (\bar{c}, v+d)$  in LS if:

- For all  $1 \le i \le n$ , we have  $((\bar{c})_i, v) \xrightarrow{d} ((\bar{c})_i, v+d)$ .

In the first case above, the *global condition* for all *m*-labeled message occurrences is the conjunction of all individual conditions, and the *global assignment* is the union of all individual assignments.

Similarly, we can define runs and  $\rightarrow^*$  for a set of time-enriched LSC charts.

**Definition 8** (Satisfaction of an LSC system) A timed trace  $\gamma \in (\Pi \cup \{\tau\} \cup \mathbb{R}_{\geq 0})^{\omega}$  satisfies (passes) an LSC system *LS*, denoted  $\gamma \models LS$ , iff  $\gamma$  corresponds to an infinite run of *LS*, and it satisfies each chart  $L_i$  in *LS* separately.

## 3.2.3 Semantics for existential charts

As mentioned in Sect. 1, unlike a universal chart which needs to be matched by each possible run of the system, an existential chart requires only one satisfying run of the system. Similar to Sect. 3.2.1, we can define the semantics for a single existential chart.

## 4 Verifying state/transition-based models against LSC requirements

A monitored LSC chart L can be used to specify a scenario-based user requirement on a state/transition-based real-time system model S (i.e., a network of timed automata). We may wish to model check S against L. However, there is no direct solution to this problem, because model checking by definition works only on state transition systems and temporal logic formulas.

To model check real-time systems against complex user requirements, a number of techniques which use (manually crafted) observer timed automata have been developed [1, 20]. We notice that a monitored LSC chart in principle functions like an observer timed automaton—the chart keeps track of the progress of the system, and reports error once there is an unexpected event or timing error in the system. In order to make use of existing observer automata-based techniques and tools for scenario-based automatic verification, we need to automatically construct a behavior-equivalent observer timed automaton  $O_L$  for chart L, let  $O_L$  observe S in a non-intrusive way, and automatically extract a temporal logic formula which together with  $O_L$  characterizes the LSC requirement.

## 4.1 LSC-to-TA translation: one automaton per chart

## 4.1.1 Basic ideas of translation

By comparing the semantic states of a timed automaton and an LSC chart, we notice that they agree on the clock valuation part, but differ on the discrete part. In a timed automaton the control switches from one location to another, whereas in an LSC chart the control progresses from one cut to a next cut. Indeed an LSC cut is comparable to a TA location—if we view all the instances of an LSC chart collectively as a whole system (i.e., an automaton), then a cut can be viewed as a control "location" of this system. Based on the above consideration, it makes sense to translate an LSC cut to a TA location.

As mentioned in Sects. 3.1.2 and 3.2.1, a simregion triggers the advancement from one LSC cut to a next cut. If we ignore the trivial cut advancement steps (i.e., the three latter cases of a "silent step"), then simregion is the only primitive semantic unit that can be stepped over to make a discrete (i.e., cut-changing) advancement step. This is very similar to a labeled

|            | LSC                   |                   | ТА                                 |

|------------|-----------------------|-------------------|------------------------------------|

| Explicitly | LSC cut               | ¢                 | TA location                        |

| specified  | Mch.	op               | ⇔                 | l <sub>min</sub>                   |

| behaviors  | $Mch. \perp$          | ¢                 | l <sub>max</sub>                   |

|            | LSC simregion         | ¢                 | TA edge                            |

|            | Message simregion     | $\Leftrightarrow$ | Synchronization transition edge    |

|            | Non-message simregion | ¢                 | Silent transition edge             |

| Implicitly | Unconstrained event   | ⇔                 | Self-loop edge                     |

| allowed    | Cold violation        | ⇔                 | Negated-guard transition edge +    |

| behaviors  |                       |                   | out-of-order sync. transition edge |

Table 1

Mapping live sequence charts to timed automata ("one-TA-per-chart")

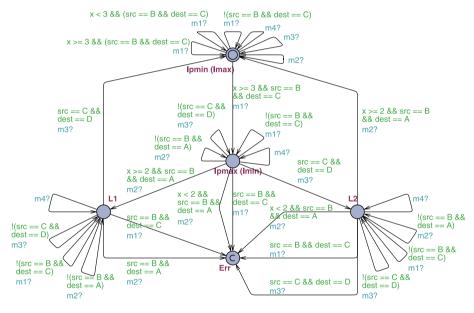

Fig. 7 The translated observer timed automaton  $O_L$  for chart L in Fig. 3 ("one-TA-per-chart" translation)

edge in a timed automaton, which connects two TA locations. Therefore, it makes sense to translate an LSC simregion to a TA edge.

The basic rules for mapping live sequence charts to timed automata are given in Table 1, which will be explained in more detail later.

For the example in Sect. 2, the original real-time system *S* consists of timed automata *A*, *B*, *C* and *D*, having channels  $m_1$ ,  $m_2$ ,  $m_3$  and  $m_4$ , and clock variable *x* (Fig. 2); and the scenario-based LSC requirement *L* is given in Fig. 3. The translated observer timed automaton for chart *L* is presented in Fig. 7.

# 4.1.2 Translating an LSC cut to a TA location

The initial cut of an LSC chart is the minimal cut of the prechart Pch. $\top$ . Starting from Pch. $\top$ , the cut advances towards Mch. $\bot$  by stepping over a simregion, or by an intra-chart coordination, or by the autonomous advancement of an instance line.

For the minimal cut Pch.  $\top$  and maximal cut Pch.  $\bot$  of the prechart (resp. Mch.  $\top$  and Mch.  $\bot$  of main chart), we assign the TA locations  $l_{pmin}$  and  $l_{pmax}$  (resp.  $l_{min}$  and  $l_{max}$ , see Table 1), respectively. The  $l_{pmin}$ ,  $l_{pmax}$ ,  $l_{min}$  and  $l_{max}$  locations correspond to the four mandatory synchronization points for all instance lines in the chart.

Each time a simregion is stepped over, we create a new cut. In comparison, the cut advancement that is caused by intra-chart coordination or the autonomous advancement of an instance line has only a "gluing" or "managerial" semantics. In order not to clutter up the translated timed automaton, in the following cases we assign two adjacent cuts the same TA location in  $O_L$ :

- *Pch*.⊥ and *Mch*.⊤; (i.e.,  $l_{pmax}$  and  $l_{min}$  are the same location in  $O_L$ , meaning that the successful completion of prechart will immediately activate the main chart. See Fig. 7)

- $Mch.\perp$  and  $Pch.\top$ ; (i.e.,  $l_{max}$  and  $l_{pmin}$  are the same location in  $O_L$ , meaning that a next round of monitoring will begin immediately after the successful completion of the main chart. See Fig. 7)

- If in chart *L*, instance  $I_i$  has no more interactions with the other instance lines (i.e.,  $I_1, \ldots, I_{i-1}, I_{i+1}, \ldots, I_n$ ) in the prechart, then the two cuts with frontiers  $(psn(loc(c)_{\langle I_1 \rangle}), \ldots, psn(loc(c)_{\langle I_{i-1} \rangle}), (Pch_bot_{L,I_i} - 1), psn(loc(c)_{\langle I_{i+1} \rangle}), \ldots, psn(loc(c)_{\langle I_n \rangle}))$  and  $(psn(loc(c)_{\langle I_1 \rangle}), \ldots, psn(loc(c)_{\langle I_{i-1} \rangle}), Pch_bot_{L,I_i}, psn(loc(c)_{\langle I_{i+1} \rangle}), \ldots, psn(loc(c)_{\langle I_n \rangle}))$ will be assigned the same TA location. Similarly for the case in the main chart.

Since there are only finitely many instance lines and simregions in an LSC chart and there are no looping structures, the number of cuts will also be finitely many.

## 4.1.3 Translating an LSC simregion to a TA edge

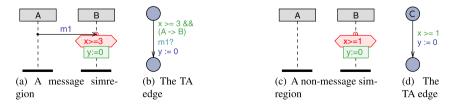

If  $s \in SR$  is a message simregion (Fig. 8(a),  $(x \ge 3, m_1, y := 0)$ ), then we map the message, condition (if any) and assignment (if any) of *s* into one edge of the TA  $O_L$  (Fig. 8(b)).

In an LSC chart, a message in  $\Sigma$  is sent from one particular instance to another one (e.g., from instance A to B). To preserve this sender/receiver information in the translated timed automaton, the TA edge will be further guarded by the predicate " $A \rightarrow B$ " (Fig. 8(b)), which is a shorthand for " $(src = A) \land (dest = B)$ ".

If  $s \in SR$  is a non-message simregion (Fig. 8(c),  $(x \ge 1, \varepsilon, y := 0)$ ), then according to the ASAP semantics, this simregion should be stepped over immediately. Since in UPPAAL timed automata, a *committed* location requires that it be exited immediately, we mark the

**Fig. 8** Translating LSC simregion to TA edge (here " $A \rightarrow B$ " denotes that instances A and B are the message sender and receiver, respectively)

source location of the translated TA edge as a committed location (Fig. 8(d), "C"-marked location).

## 4.1.4 Incremental construction of the TA

In Sects. 4.1.2 and 4.1.3 we showed how to translate a single cut and simregion to a TA location and edge, respectively. When translating an entire chart into a timed automaton, we need to exploit the structural information of LSC to conduct incremental translation.

As mentioned in Sect. 3.1.2, simregion is the primitive semantic unit for triggering cut advancements. At a given cut there might be more than one next simregion that can be stepped over. Each simregion should correspond to an outgoing edge from the TA location that corresponds to the given cut. All of these simregions should be translated to TA edges that share the same common "source cut." But before we can do this, we should determine how all the simregions are partially ordered in a chart, and how these simregions and the cuts are partially ordered.

In Sect. 3.2 we showed how to determine the preorder relation  $\preccurlyeq$  on the set loc(L) of locations of chart L. Now the relation  $\preccurlyeq$  on loc(L) can be lifted up to a partial order  $\preccurlyeq'$  on  $(SR \cup Cuts)$  as follows:

$$\forall s_1, s_2 \in (SR \cup Cuts) . (s_1 \preccurlyeq s_2 \Leftrightarrow \exists l_1 \in loc(s_1), l_2 \in loc(s_2) . l_1 \preccurlyeq l_2).$$

For instance in Fig. 3, the partial order  $\preccurlyeq'$  among the three simregions  $s_1$  (middle),  $s_2$  (left) and  $s_3$  (right) is:  $s_1 \preccurlyeq' s_2$ , and  $s_1 \preccurlyeq' s_3$ .

Assume that a TA location *l* has already been created for the current LSC cut (Fig. 9(a), cut  $\{s_1 = (x \ge 3, m_1, \varepsilon)\}$ , and Fig. 9(b), TA location *l*). Without loss of generality, we assume that there are two immediately following simregions  $s_2$  and  $s_3$ .

If  $s_2$  and  $s_3$  are both message simregions (Fig. 9(a)), then the two new TA edges will be appended to location *l*. The LSC and TA semantics coincide that there are two possible orderings of the execution of the two transitions. Let the two new edges be  $(l_1, l_2)$  and  $(l_3, l_4)$ , respectively. Then  $l_1$  and  $l_3$  will be superposed on *l* (Fig. 9(b)). The cut will be advanced accordingly.

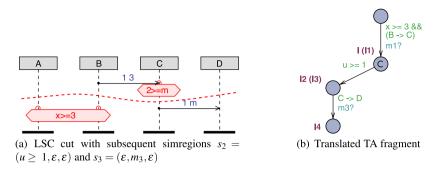

If  $s_2$  is a non-message simregion that spans across instance lines A and B, e.g.,  $(u \ge 1, \varepsilon, \varepsilon)$  (Fig. 10(a)), then according to the ASAP semantics,  $s_2$  will be stepped over immediately, and  $s_3$  will follow, but cannot be the other way around. When appending the corresponding two edges  $(l_1, l_2)$  and  $(l_3, l_4)$  to the TA, we mark the source location  $l_1$  as a committed location, and superpose it on l (Fig. 10(b), edge  $(l_1, l_2)$ ). Note that in this case  $l_2$  may not be superposed on l. Therefore, there is only one possible ordering of edges  $(l_1, l_2)$  and  $(l_3, l_4)$  (Fig. 10(b)).

Fig. 9 TA edge construction for two subsequent message simregions

Fig. 10 TA edge construction for a subsequent message and non-message simregions

Fig. 11 TA edge construction for two subsequent non-message simregions

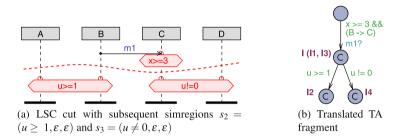

If  $s_2$  and  $s_3$  are both non-message simregions, e.g.,  $(u \ge 1, \varepsilon, \varepsilon)$  and  $(u \ne 0, \varepsilon, \varepsilon)$ (Fig. 11(a)), then according to the ASAP semantics, both  $(l_1, l_2)$  and  $(l_3, l_4)$  will be executed immediately, therefore there are again two possible orderings of the execution of the two transitions (Fig. 11(b)).

## 4.1.5 Implicitly allowed behavior

In addition to the *explicitly* specified behaviors, an LSC chart also has behaviors that are *implicitly* allowed, e.g., those due to unconstrained events and cold violations (Table 1).

Let  $\Pi$  correspond to the set of possible messages in the system model *S* (i.e., a network of timed automata), and  $\Sigma \subseteq \Pi$  be the set of messages in chart *L*. Clearly, messages in  $(\Pi \setminus \Sigma)$  are not constrained by chart *L*. For each message in  $(\Pi \setminus \Sigma)$ , we add a corresponding self-loop edge to each non-committed location *l* of the translated TA  $O_L$ . For example in Fig. 7, at location  $l_{pmin}$  the unconstrained events correspond to the edges labeled with  $m_4$ ,  $[!(src == B \&\& dest == C)]m_1$ ,  $[!(src == B \&\& dest == A)]m_2$  and  $[!(src == C \&\& dest == D)]m_3$ . Note that the latter two edges will be merged with some cold violation edges that will be explained shortly, thus giving rise to the  $m_2$ - and  $m_3$ -labeled edges, respectively.

According to the LSC semantics, cold violations in the prechart or main chart are not failures. Rather they just bring the chart back to the prechart minimal cut. To model this, for a cut *c* and each following simregion *s* that has a cold condition *g*, we add edges from the corresponding TA location *l* to  $l_{pmin}$  to correspond to the  $\neg g$  conditions (of DNF form) (Fig. 7, the edge labeled with  $[(x < 3) \&\& (src == B \&\& dest == C)]m_1$  from  $l_{pmin}$  to  $l_{pmin}$ ). Similarly, given a cut *c* in the prechart, for each *m*-labeled message that occurs in *L* but does not follow *c* immediately (i.e., it violates the event partial order), we also add a

corresponding TA edge  $(l, l_{pmin})$  (Fig. 7, the edges labeled with  $[(src == B \&\& dest == A)]m_2$  and  $[(src == C \&\& dest == D)]m_3$  from  $l_{pmin}$  to  $l_{pmin}$ ).

# 4.1.6 Undesired behavior

The construction of the observer TA so far considers only the legal (or admissible) behaviors. When the current configuration (c, v) is in the main chart, if an observed message is not enabled at cut c (i.e., it is an out-of-order message), or the hot condition of the simregion that immediately follows c evaluates to false under v, then there will be a hot violation. In this case, we add a dead-end (sink) location Err in the TA, and for each such hot violation we add an edge to Err (Fig. 7).

# 4.1.7 Invariant activation mode

According to the LSC semantics, under the invariant mode the prechart is being continuously monitored. Normally we need to maintain multiple incarnations of the chart. In this way, a given message sequence will not be incorrectly rejected by the chart (i.e., there is no false negative). For instance, given the chart in Fig. 3, and given a message sequence  $m_1 \cdot m_1 \cdot m_2 \cdot m_3$  (assuming that the message guards in Fig. 3 are all satisfied), although the first incarnation of the chart hot-violates this sequence (i.e., the second  $m_1$  violates the message partial order in the main chart), the second incarnation works well with it (i.e., the latter three messages  $m_1 \cdot m_2 \cdot m_3$  match the chart).

To enforce the LSC semantics under the invariant activation mode, for each message occurrence that appears in *Pch* as a minimal event (i.e., an event that is minimal in the event partial order induced by the chart), we add a corresponding self-loop to location  $l_{pmin}$  (Fig. 7, the  $[(x \ge 3) \&\& (src == B \&\& dest == C)]m_1$ -labeled self-loop edge at  $l_{pmin}$ ). We call this kind of handling *prechart pre-matching*.

# 4.2 Complexity

Let the number of simregions that appears in L be n. In the worst case, the number of locations in the translated observer TA  $O_L$  is  $2^n + 1$ . We have this exponential complexity when L consists of only the prechart or the main chart, and the messages in L are totally unordered.

The number of outgoing edges from a location l of  $O_L$  depends on: (1) the number of unconstrained events, ue; (2) the number of the following simregions in the corresponding cut c of L, fs; (3) the length of the condition (in case the condition evaluates to false), lc; and (4) the number of messages that cause violations of the chart, cv. Therefore, the number of outgoing edges from a TA location has complexity O(ue + fs + lc + cv).

Since the LSC simregions are directly copied as TA edges,  $O_L$  has the same numbers of synchronization channels (message labels) and clock variables as L.

# 4.3 Equivalence of LSC and TA

If in the translated timed automaton  $O_L$  of chart L we ignore the undesired and implicitly allowed behaviors, i.e., we ignore the edges that correspond to hot violations, unconstrained events, cold violations, and prechart pre-matching, then we have:

**Theorem 1** If a configuration (c, v) of L corresponds to a semantic state (l, v) of  $O_L$ , then: (1) each simregion s that follows (c, v) in L uniquely corresponds to an outgoing edge (l, l')in  $O_L$ ; and (2) the target configuration (c', v') of s in L uniquely corresponds to the target semantic state (l', v') in  $O_L$ .

Theorem 1 says that each LSC configuration is uniquely mapped to a semantic state of the observer timed automaton, and each LSC simregion is uniquely mapped to an edge of that automaton.

If in the LSC semantics (Sect. 3.2.1) we ignore the silent steps that are caused by intrachart coordinations and autonomous advancements of instance lines, then based on Theorem 1, we have the following theorem:

**Theorem 2** For any trace tr in  $O_L$ :  $tr \models L \Leftrightarrow (O_L, tr) \models (l_{min} \rightsquigarrow l_{max})$ .

Theorem 2 says that a trace in the observer timed automaton of an LSC chart satisfies that chart if and only if the trace satisfies the "leads-to" property  $(l_{min} \rightarrow l_{max})$  in that automaton. Alternatively, it indicates that  $O_L$  has exactly the same set of *legal* traces as L.

As we can anticipate, the prechart pre-matching mechanism in Sect. 4.1.7 does introduce undesired behaviors and non-determinacy. For instance in Fig. 7, the message sequence  $tr = m_1 \cdot m_1 \cdot m_2 \cdot m_3$  could be an accepted trace in  $O_L$  (assuming that all message guards are satisfied). But since its sub-sequence  $tr' = m_1 \cdot m_1$  can be rejected (i.e., leading to a hot violation), so tr does not really satisfy L. However, it coincides that this particular trace tr in the model  $O_L$  does not satisfy the CTL property  $(l_{min} \rightsquigarrow l_{max})$  as well.

The syntax and semantics of timed automata are given in Appendix B. The proofs of theorems in Sect. 4 and the lemma for them can be found in Appendix C.

# 4.4 Composing the observer automaton with the original system

With the development so far in this section (Sect. 4), the set X of clocks can be viewed as "private" clocks of the LSC chart L, i.e., L can both read and *reset* these clocks. When we use the observer timed automaton  $O_L$  to observe the original system S, then the set  $C_S$  of clocks in S will also be visible to (but cannot be reset by)  $O_L$ . To this end, the definition of the clock valuation part of a configuration of L will be extended accordingly.

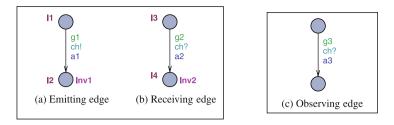

When composing  $O_L$  with S, we wish that  $O_L$  would "observe" S in a *timely* and *non-intrusive* manner. A natural idea is to let the synchronization channels in  $O_L$  (and accordingly the relevant channels in S) be broadcast channels to achieve this goal. However, this is not possible because UPPAAL has a restriction that broadcast channels cannot be guarded by timing constraints. To solve this problem, we propose to use spying techniques such that the translated observer TA will be notified of each message synchronization in the original system *immediately after* it occurs there. Specifically, for each channel  $ch \in \Pi$ , we make the following modifications:

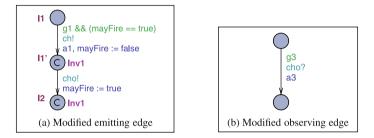

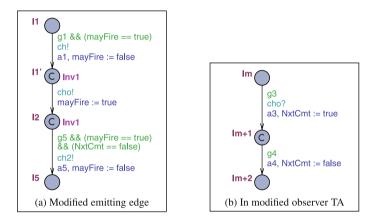

- (1) In S (e.g., Fig. 12(a)–(b)), for each edge (l<sub>1</sub>, l<sub>2</sub>) that is labeled with ch!, we add an intermediate committed location l'<sub>1</sub> and a cho!-labeled edge in between edge (l<sub>1</sub>, l<sub>2</sub>) and location l<sub>2</sub>. Here cho is a dedicated fresh channel which aims to notify O<sub>L</sub> of the occurrence of the ch-synchronization in S. The location invariant (if any) of l<sub>2</sub> will be copied on to l'<sub>1</sub>. Furthermore, we use a global boolean flag variable (i.e., a binary semaphore) mayFire to further guard the ch-synchronization. This semaphore is initialized to true at system start. It is cleared immediately after the ch-synchronization in S is taken, and it is set again immediately after the cho-synchronization is taken (Fig. 13(a)).

- (2) In  $O_L$  (e.g., Fig. 12(c)), each synchronization label ch? is renamed to cho? (Fig. 13(b)).

Fig. 12 Coupling emitting/receiving edges in original system model S and the observing edge in observer timed automaton  $O_L$

Fig. 13 Edge modifications for Fig. 12

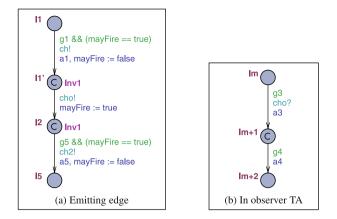

If *L* has non-message simregions, then  $O_L$  contains corresponding committed locations. If in a certain state both  $O_L$  and some timed automata in *S* are in committed locations (e.g.,  $l_{m+1}$  in Fig. 14(b), and  $l_2$  in Fig. 14(a)), there will be a race condition. But according to the ASAP semantics of *L*, the (internal action) edge in  $O_L$  has higher priority. To this end, for each edge  $(l_i, l_{i+1})$  in  $O_L$ , if  $l_{i+1}$  is a committed location, then we add "*NxtCmt* := true" to the assignment of the edge, otherwise we add "*NxtCmt* := false". Here the global boolean flag variable (i.e., a binary semaphore) *NxtCmt* denotes whether the observer TA will be in a committed location (Fig. 15(b)). This semaphore is initialized to false at system start. Accordingly, for each ch-labeled edge  $(l_i, l_{i+1})$  in *S* where  $ch \in \Pi$  and  $l_i$  is a committed location, we use "*NxtCmt* == false" to strengthen the condition of the edge (Fig. 15(a)).

Our method of composing the observer timed automaton  $O_L$  with the original system model S is similar to that of [15]. While their method works only when the target state of a communication action is not a committed location in the original model, in our method, due to the first locking mechanism (using *mayFire*), we have no restrictions on whether a location in S is a normal, urgent or committed one. Broadcast channels can be handled the same way as binary synchronization channels in our method. Furthermore, due to the second locking mechanism (using *NxtCmt*), we guarantee the enforcement of the ASAP semantics in  $O_L$ .

Our method involves only syntactic scanning and manipulations. For each  $ch \in \Pi$ , we need to introduce a dedicated fresh channel cho. For each occurrence of the emitting edge ch!, we need to introduce a fresh committed location in *S*. Moreover, we need two global boolean flag variables (*mayFire*, *NxtCmt*) as the binary semaphores.

## Example of Sect. 2 Continued

After modifying *S* and the automatically generated observer TA  $O_L$ , we get the composed network of instrumented TAs  $(S' \parallel O'_L)$  (Fig. 16 and 17). Note that in Fig. 17 each channel name has been suffixed with an "o", e.g., m1 becomes m10.

Fig. 14 Race condition for Fig. 13 due to a non-message simregion in LSC chart (and thus a committed location  $l_{m+1}$  in observer timed automaton)

Fig. 15 Further modifications for Fig. 14

## 4.5 Verification problems

After the modifications, the original system model *S* becomes *S'*, and the observer timed automaton  $O_L$  for chart *L* becomes  $O'_L$ . Let the minimal and maximal cuts of the main chart of *L* correspond to locations  $l_{min}$  and  $l_{max}$  of  $O'_L$ , respectively. Recall that the UPPAAL "leads-to" property ( $\phi \rightsquigarrow \varphi$ ) stands for  $A \Box (\phi \Rightarrow A \Diamond \varphi)$ , where  $\phi$  and  $\varphi$  are state formulas.

When *L* is a universal chart, we have the following main theorem:

**Theorem 3**  $S \models L \Leftrightarrow (S' \parallel O'_L) \models (l_{min} \rightsquigarrow l_{max}).$

Theorem 3 says that a TA-modeled real-time system S satisfies a universal LSC chart requirement L if and only if the parallel composition of the (instrumented) system and the observer timed automaton satisfies the "leads-to" property  $(l_{min} \rightsquigarrow l_{max})$ . This indicates that the problem of model checking real-time systems against universal LSC chart requirements can be equivalently transformed into a CTL real-time model checking problem in UPPAAL.

Fig. 16 The modified model S' of the original real-time system in Fig. 2(a)-(d)

Fig. 17 The modified version of the translated observer timed automaton  $O'_{L}$  (Fig. 7) of the chart in Fig. 3

When L is an existential chart, we have another main theorem:

**Theorem 4**  $S \models L \Leftrightarrow (S' \parallel O'_L) \models \mathsf{E} \Diamond l_{max}.$

Theorem 4 says that a TA-modeled real-time system S satisfies an existential LSC chart requirement L if and only if the parallel composition of the (instrumented) system and the observer timed automaton satisfies the reachability property  $E \Diamond l_{max}$ .

Furthermore, it is possible to check whether a system *S* satisfies multiple existential charts  $L_1, L_2, \ldots, L_m$  simultaneously by checking the formula  $E \Diamond (l_{1,max} \land l_{2,max} \land \ldots \land l_{m,max})$ , where  $l_{i,max}$  denotes the location in observer TA  $O'_{L_i}$  that corresponds to the maximal cut of the main chart of existential chart  $L_i, 1 \le i \le m$ .

## Example of Sect. 2 Continued

For the composed network of instrumented timed automata in Figs. 16 and 17, we check in UPPAAL the property  $(l_{min} \rightsquigarrow l_{max})$ , and it turns out to be satisfied. This indicates that *S* does satisfy the requirements that are specified in *L*.

If in L the condition of  $m_2$  is changed from  $x \ge 2$  to e.g.  $x \ge 4$ , then the property is found not satisfied. There will be a counterexample, e.g., when  $O'_L$  gets to location L2 (Fig. 17), but the value of clock x falls in [3, 4), then it will get stuck in location Err and will never be able to arrive at location  $l_{max}$  thereafter.

## 5 Verifying object interaction-based models against LSC requirements

In addition to being used as a property specification language, LSC can also be used as a scenario-based behavioral modeling language (i.e., as a high-level "programming" language [18]). When some LSC charts are used for behavioral modeling and some others are used for property specification, it will be possible to verify scenario-based LSC models against scenario-based LSC requirements. Clearly, this contributes to earlier validation of the prototyped systems.

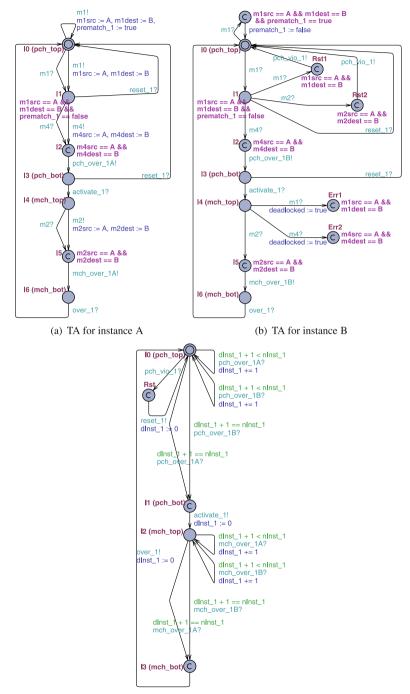

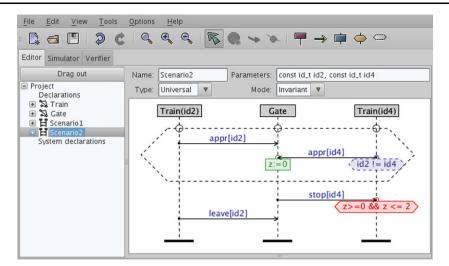

5.1 LSC-to-TA translation: one automaton per instance line

## 5.1.1 Motivation